Blog

TSMC introduces A13 node; says no need for high-NA through 2029

“We continue to be able to harvest the benefit from current EUV,” said Zhang said, which would continue to be the case through 2029. Zhang added that TSMC’s A13 chip will go into production in 2029

The A13 process is a direct shrink of TSMC’s A14 node announced in 2025, which provides 6% area savings from A14. The A13 design rules are fully backward compatible with A14..

“At TSMC, we understand our customers are always looking ahead to their next innovation and they come to us for a reliable stream of new silicon technologies, like A13, meticulously engineered to be ready for high-volume production right when their visionary new designs demand them,” said TSMC CEO C.C. Wei. “TSMC’s advanced process technologies lead the industry in density, performance and power efficiency, and we continually strive to make them even better for our customers’ future products, ensuring customers’ success as their most reliable technological partner.”

TSMC previewed its A14 platform enhancement A12, which features Super Power Rail technology to provide backside power delivery for AI and HPC applications. A12 is also scheduled to enter production in 2029.

TSMC has advanced its 2nm platform with the introduction of N2U, which employs design-technology co-optimization to reach speed gains of 3-4% or power reduction of 8-10% and a 1.02-1.03X logic density improvement from N2P.

A balanced option for AI, HPC, and mobile applications leveraging the process maturity and strong yield performance of the 2nm technology platform, N2U is scheduled for production in 2028.

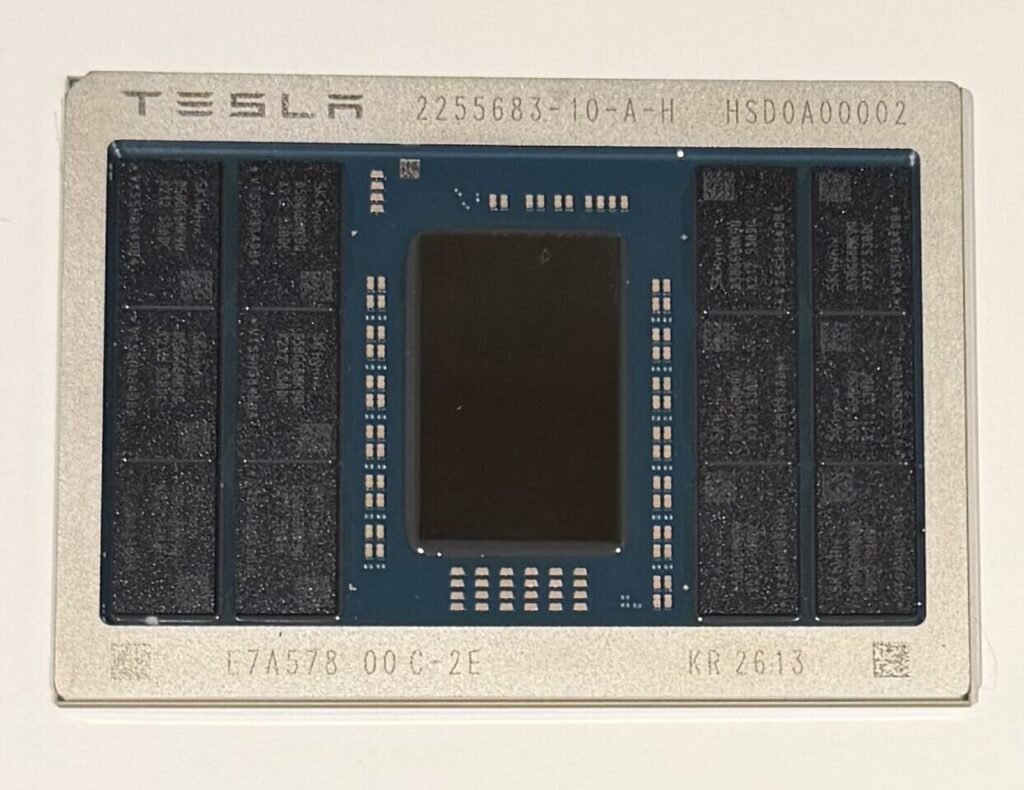

To support AI demand for more computing power and memory in a single package, TSMC continues to expand its Chip on Wafer on Substrate (CoWoS®) technology to integrate more silicon.

The Company is now producing 5.5-reticle size CoWoS and planning for even larger versions. A 14-reticle size CoWoS, capable of integrating approximately 10 large compute dies and 20 HBM stacks, is slated for production in 2028.

This will be followed by an expansion to beyond 14 reticles in 2029. These new offerings provide customers with more options for AI compute scaling and complement TSMC’s 40-reticle size SoW-X System-on-Wafer technology also expected in 2029.

TSMC is also offering its TSMC-SoIC® 3D chip stacking technology on its most advanced technology platform, with A14-to-A14 SoIC set to be available for production in 2029. It will provide 1.8X higher die-to-die I/O density compared with N2-on-N2 SoIC, supporting higher bandwidth of data transfer between stacked chips.

TSMC’s Compact Universal Photonic Engine (TSMC-COUPE™) is set to reach a key milestone with a true co-packaged optics solution using COUPE on substrate beginning production in 2026. By integrating the COUPE optical engine directly inside the package, TSMC achieves 2X power efficiency and 10X latency reduction versus a pluggable version on the circuit board.

The technology is featured in a 200Gbps micro-ring modulator, a highly compact and energy-efficient solution to move data between racks in data centers.

ADAS and autonomous vehicles require leading-edge technologies along with stringent quality and reliability standards. Physical AI applications, such as humanoid robots, are adopting similarly demanding requirements.

To address these needs, TSMC announced N2A, the first automotive-grade process technology with nanosheet transistors. N2A provides 15-20% speed gain at the same power compared with N3A and is scheduled to complete AEC-Q100 qualification in 2028.

Furthermore, TSMC is making “Auto-Use” design kits available within its N2P process design kit (PDK), enabling customers to factor in automotive usage conditions in the design. This allows customers an earlier design start before N2A process is fully qualified.

TSMC’s efforts to speed up automotive product cycles are already paying off for customers as N3A enters production in 2026. With the N3 “Auto Early” program, customers were able to start designs in 2023, and today more than 10 products are planned on N3A technology to make automobiles smarter, greener, and safer for consumers.

TSMC claims to be the first to bring high voltage technology into the FinFET era in 2026 with its N16HV process aimed at display driver applications.

For smartphone display drivers, N16HV will increase gate density by 41% and reduce power by 35% compared to TSMC’s N28HV process. For near-eye displays, N16HV can shrink die area by 40% and reduce power by over 20%, enhancing the usability of applications such as smart glasses.