Blog

How VisualSim Architect Models UCIe Chiplet Latency and Multi-Die CPU Tradeoffs

Designing virtually is the least costly and most effective way to design complex systems. VisualSim Architect from Mirabilis Design lets engineers combine and test complex systems like cars, satellites, all the way down to chiplets. Systems can become even more complex when combining different components from different vendors. VisualSim Architect helps simulate that system ahead of time.

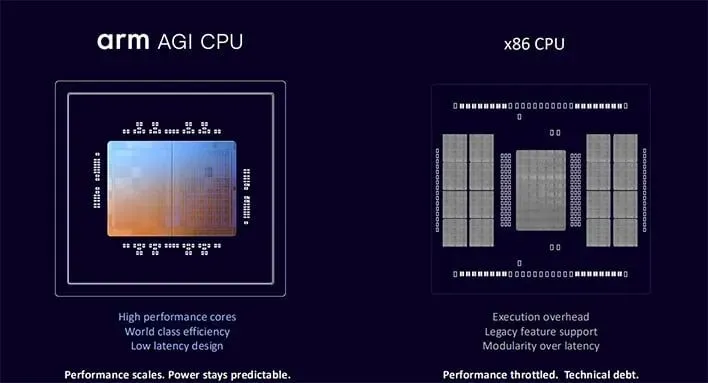

System modeling isn’t just component assemblies, but also the flow, or the communication, between them all. Chiplet UCIe modeling accuracy is essential in any design. Predictability and testing early on save time and money. But, how is accuracy dealt with when integrating chiplets from different vendors?

In the video, Deepak Shankar, Founder of Mirabilis Design, delves into the latency of transmitting 64 bytes versus 128 bytes across the same system. He brought forth how 128 might be more efficient in some cases, but not enough to go beyond 64. Simulating a UCIe interface here allowed the exploration of results with simple parameters injected into the system.

In a more complex example, Shankar shows a 2-die vs. a 4-die CPU model. In both examples, applications run on the CPUs, showing power demand, heat generated, and latency over time. The 4-die CPU configuration experienced a significant increase in latency over the 2-die configuration. This reveals that parameters inside the system model cause the increase in latency. Optimization ahead of time is the true benefit of system simulation. VisualSim Architect is essential in the design process.