Blog

Capacity constraints | Electronics Weekly

3nm capacity—currently dominated by TSMC—has become even more constrained,

Nvidia preemptively secured large volumes of 4/3 nm wafer capacity, CoWoS packaging, as well as key materials such as T-glass, substrates, PCBs, HBM, and SSDs.

The consumption of wafer and packaging resources per chip is increasing exponentially as the demand for AI compute drives larger chip sizes.

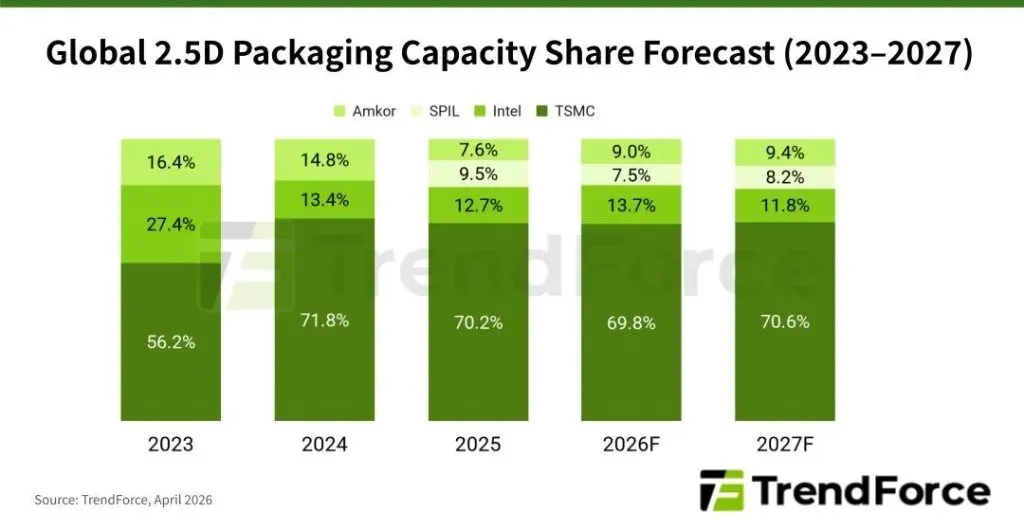

Despite TSMC’s capacity expansion, CoWoS has remained in short supply since 2023, prompting customers to seek alternative capacity sources.

OSAT providers such as SPIL and Amkor have benefited from this spillover demand, and alternative technologies like EMIB and FOEB are also gaining traction, with Intel leveraging its U.S.-based manufacturing advantage.

TrendForce expects that the severe shortage in global 2.5D packaging capacity will begin to ease slightly by 2027, aided by order spillover and TSMC’s plan to expand CoWoS capacity by over 60% by 2027.

AI compute chips are rapidly transitioning from 4 nm to 3 nm between late 2025 and 2026.

Smartphone and PC processors have yet to migrate en masse to 2nm, resulting in a short-term concentration of high-performance demand on 3 nm.

For 3nm there is a single-supplier dynamic and TSMC is accelerating the construction of new 3nm fabs to alleviate the imbalance.

As additional capacity comes online, global 3 nm capacity is expected to surpass 5/4 nm by the end of 2026 and become the second-largest process node after 28 nm by 2027.