Blog

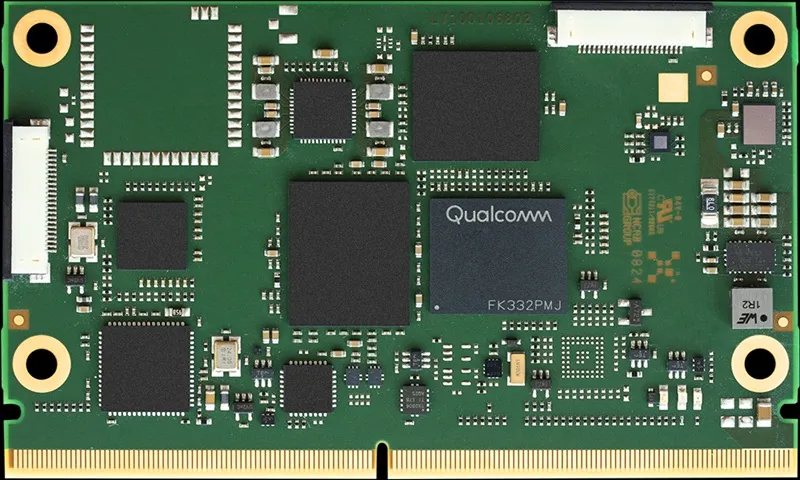

LPDDR5/5X SPD with Enhanced Mode Switching support

Bill Gervasi, of Monolithic Power Systems, and Chair of the JEDEC SPD Task Group, commented:

“Reducing power consumption has become imperative for computing systems as the use of AI and other demanding applications accelerate. The updates to the JESD406-5 standard are an important enabler for systems to optimise performance while maintaining a lower power profile.”

Jedec highlights that LPDDR5/5X memory devices are capable of supporting two sets of timing parameters. Both a full speed mode and a reduced speed mode that consumes less power.

This feature allows for longer battery life for mobile devices, it says, a common application for LPDDR5/5X chips and modules.

Now, the updated JESD406-5 standard documents key parameters for calculating the switching time between the fast and low power modes. This feature will help with efficiency and allowing higher system performance.

JESD406-5D is available for free download from the JEDEC website.

Image: Micron LPDDR5 memory