Blog

Intel Core Ultra “Nova Lake-S” Desktop Core Configurations Surface

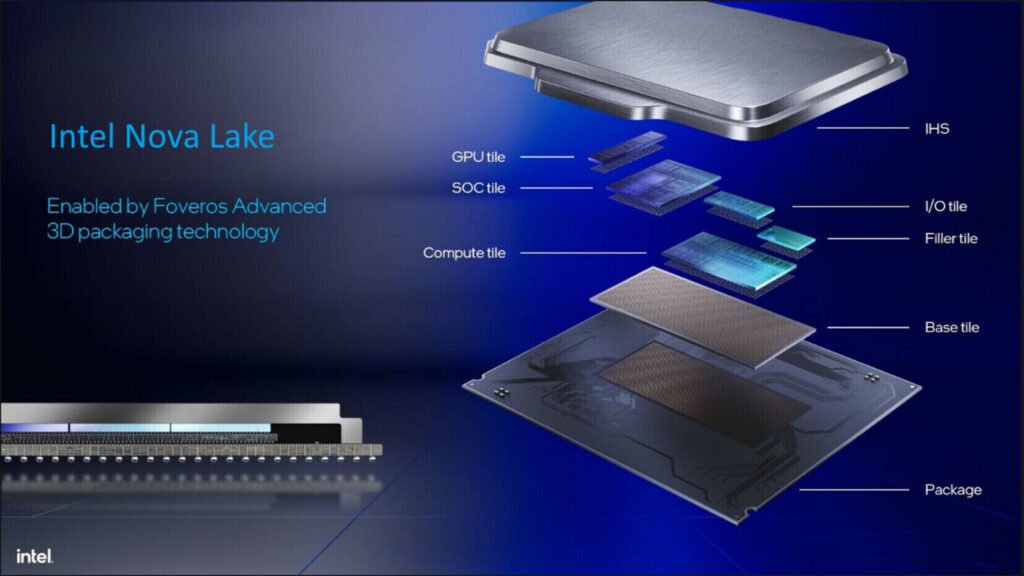

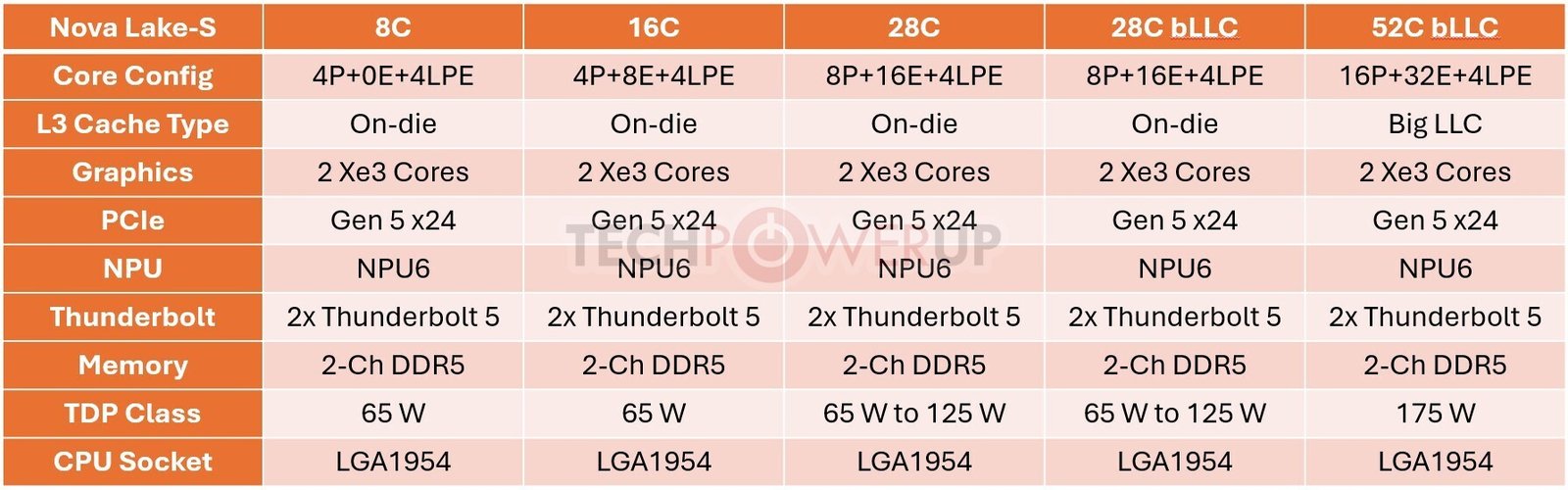

Intel intends LGA1954 to have longevity spanning several processor generations lasting till the end of the decade. The Core Ultra Series 4 will span a wide range of price-points, starting with Core Ultra 3, having the least core-count, going all the way up to Core Ultra 9 (probably X9). Perhaps the most interesting bit of news is the introduction of dual-die processors. These are SKUs with two Compute tiles connected to the SoC tile. This allows Intel to achieve extremely high CPU core counts. Since this is essentially the same approach to high core counts as AMD, both Compute tiles have equal access to memory and PCIe.

The series begins with the first kind of SKUs, probably Ultra 3, with a 4P+0E+4LPE cores, so that’s four “Coyote Cove” performance cores, no E-cores within the main CPU complex, but four “Arctic Wolf” low-power island E-cores in the SoC tile. The total core-count is therefore 8.

The second kind of SKUs come with a 4P+8E+4LPE configuration: four “Coyote Cove” performance cores, eight “Arctic Wolf” E-cores within the compute complex, sharing L3 cache with the P-cores; and four “Arctic Wolf” low-power island E-cores, for a total core-count of 16.

The third kind sees a steep rise in core counts, now up to 8P+16E+4LPE; that’s eight “Coyote Cove” performance cores, sixteen “Arctic Wolf” E-cores within the main CPU complex, sharing L3 cache with the P-cores, and those four low-power island E-cores, pushing core-count to 28.

Here’s where things get interesting. Intel is introducing the concept of bLLC, or “big last-level cache,” its answer to AMD’s 3D V-Cache technology. It sees the introduction of an in-package cache die that augments the on-die L3 cache that’s part of the CPU complex. There will be one kind of SKUs with 8P+16E+4LPE core configuration with this bLLC. Intel might introduce a new brand extension to denote this SKU separately from the regular 8P+16E+4LPE SKUs. The recent introduction of “Core Ultra X9” and “Core Ultra X7” with “Panther Lake” mobile processors could provide some clue.

Perhaps the most astounding development is the fabled extreme core-count desktop processor featuring two Compute tiles with bLLC dies on top. This chip has an astounding 16P+32E+4LPE core-configuration, and Intel could create SKUs that max-out this core-count, or come up with cut-down configurations such as 16P+24E+4LPE.

All SKUs will come with certain common on-die components and I/O. All chips will feature a next-generation NPU6 device that meets Microsoft Copilot+ local acceleration hardware requirements. Every SKU will come with preparation for two Thunderbolt 5 or USB4 V2 ports (80 Gbps bidirectional or 120+40 Gbps asymmetric), however, implementation of these ports will depend on motherboard vendors, based on chipset SKU. All chips will feature a 2-channel DDR5 memory interface, and Intel is expected to increase the native memory speeds, maximum memory capacity, and offer native support for 4-rank DDR5 DIMMs. The integrated graphics solution is based on the Xe3 “Celestial” graphics architecture, with no more than 2 Xe3 cores, which should match or exceed graphics performance of the current “Alchemist” based iGPU powering “Arrow Lake-S.”