Blog

Driving Innovation in 3D IC: Chiplet Summit

3D IC solutions based on chiplets provide many advantages, such as enabling designs that exceed the reticle limit for a monolithic die. Kevin Rinebold, Technology Manager 3D IC Solutions at Siemens EDA, presents issues and solutions for designers of 3D ICs (watch the video above).

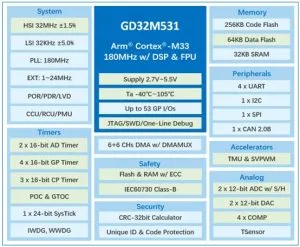

Transistors are shrinking, but the number of transistors in a die is growing — especially for high-performance processors, GPUs, and neural processing units (NPUs). Also, the gap is widening between compute and memory speeds (Fig. 1).

The difference in silicon technologies used for compute and memory speeds is changing how solutions are designed. High-bandwidth-memory (HBM) chiplets allow wide, fast RAM to be interfaced with compute die that use smaller transistors. This mix would not work on a monolithic die.

Moving to a chiplet-based, 3D IC packaged system provides a number of benefits, but more design considerations come into play for a system that’s already very complex (Fig. 2). Details like connectivity have led to the development of interfaces such as the UCIe Consortium’s Universal Chiplet Interconnect Express (UCIe).

3D ICs make it possible to build advanced artificial-intelligence (AI) chips. However, designing, testing, and delivering them requires EDA and product lifecycle tools like those available from Siemens EDA. They take advantage of advanced, multi-physics modeling as well as standards like UCIe.