Blog

Intel Core Ultra Series 3 “Panther Lake-H” Die Annotated

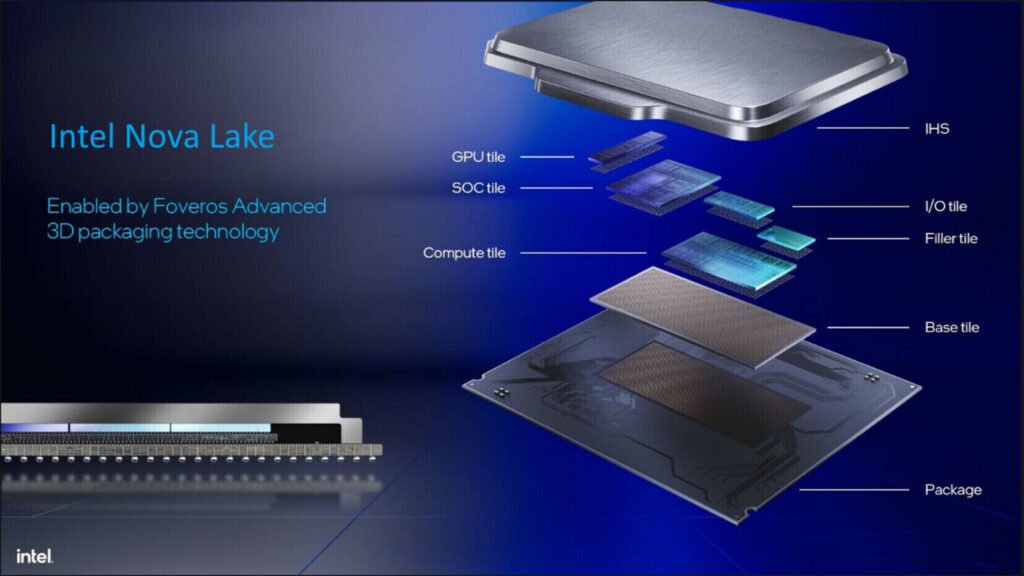

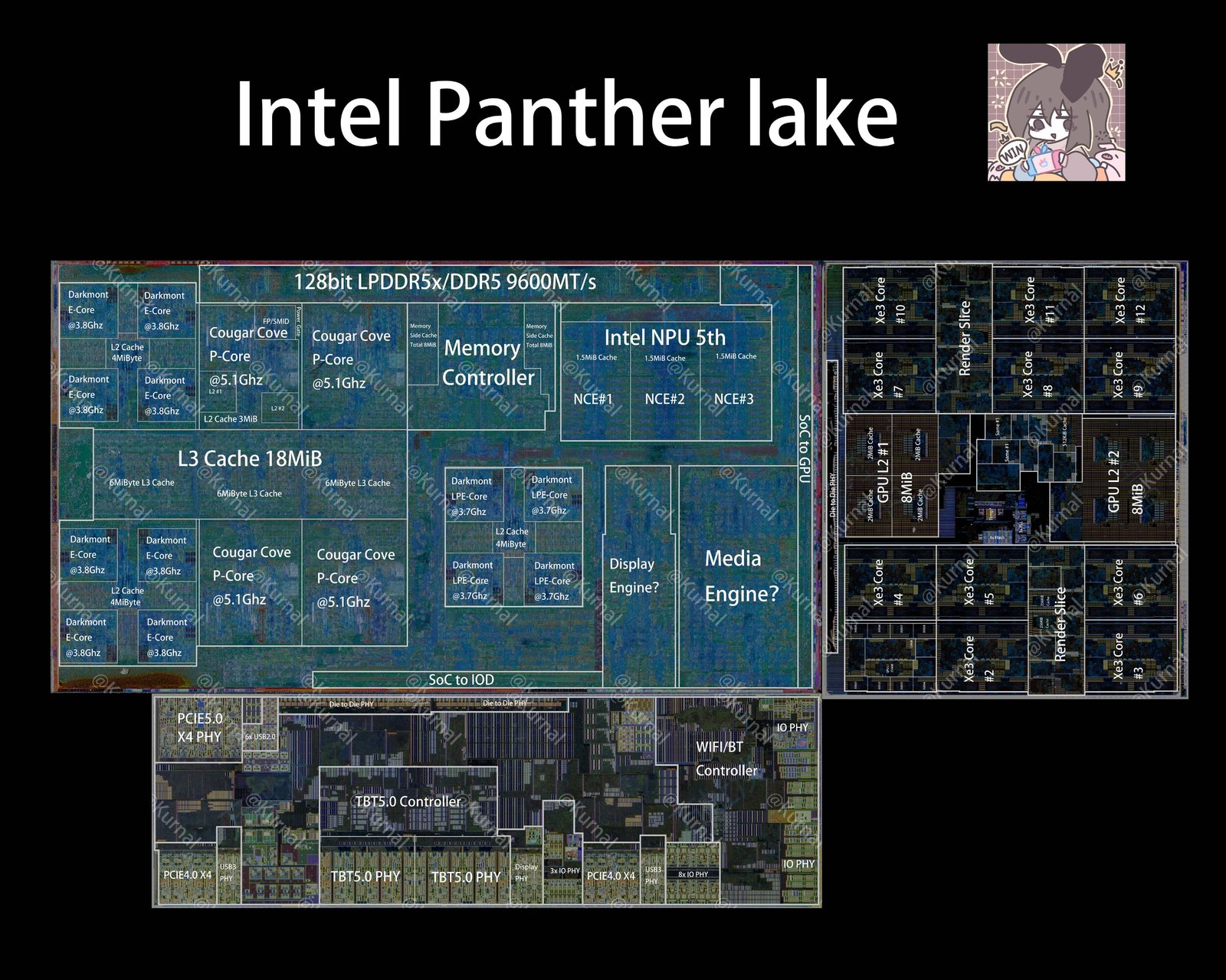

The SoC tile is built on the Intel 18A foundry node. On the mainstream notebook “Panther Lake-H” processor variants, such as the one annotated below, the Graphics tile contains 4 Xe cores, and is built on the Intel 3 foundry node. On the ultraportable “Panther Lake-U” processor with powerful integrated graphics meant for devices lacking discrete GPUs, the Graphics tile has 12 Xe cores, and is built on the TSMC N3E node. The I/O tile continues to be built on the same TSMC N6 node as the ones on previous-generation “Arrow Lake” processors.

“Panther Lake-H” contains a total of four tiles—a base tile built on Intel 22 nm that serves as an interposer, enabling high-density microscopic wiring among the tiles stacked on top; the Compute tile, the Graphics tile, and the I/O tile. Although the three tiles are joined at the hip making up a non-rectangular shape, Intel uses structural silicon, called Filler tiles, to create an even, rectangular chip shape for uniform contact with the cooling solution.

The Compute tile is by far the largest of the three tiles, it measures 14.32 mm x 8.04 mm (115 mm²). It contains the chip’s 16 CPU cores, that’s 6P+8E+4LPE. The main compute complex contains six “Cougar Cove” performance cores (P-cores), and two “Darkmont” efficiency core clusters (E-core clusters) connected by a ringbus, and sharing an 18 MB L3 cache.

Each “Cougar Cove” P-core has 3 MB of dedicated L2 cache; while each of the two “Darkmont” E-core clusters shares 4 MB of L2 cache among the four cores in the cluster. The low-power island E-cores are not part of the CPU complex’s ringbus, and although there’s on the same physical tile, they are separate, and talk to the CPU complex over the tile’s internal switching fabric. While the P-cores boost up to 5.10 GHz, and the E-cores up to 3.80 GHz, the low-power island E-cores have significantly lower base frequencies, and boost only up to 3.70 GHz. The low-power island E-cores are clumped into a 4-core cluster, with 4 MB of L2 cache shared among the four cores.

Besides CPU cores, the Compute tile has the processor’s main memory controller, which is cushioned by an 8 MB memory-side cache. The tile also contains the main memory I/O, supporting 2-channel DDR5 and LPDDR5X at up to 9600 MT/s. Then there’s Intel’s NPU 5, the new-generation neural processing unit, with three neural compute engines (NCEs), each with 1.5 MB cache, which together makes up 4.5 MB of scratchpad RAM. The remaining die-space on the Compute tile probably contains the media engine and display engine, two key components of the iGPU.

Next up, is the Graphics tile. The one pictured here is the larger model built on TSMC N3E, and measures 8.14 mm x 6.78 mm (55.18 mm²). This tile contains the front-end of the GPU, and 12 Xe cores, besides 16 MB of L2 cache. The iGPU of “Panther Lake” is based on the Xe3 “Celestial” graphics architecture.

Lastly, there’s the slender, though all-important I/O tile. This one measures 12.44 x 4 mm (49.76 mm²), and is built on the TSMC N6 foundry node. This tile contains a PCIe root complex, and a fully-integrated Thunderbolt 5 (or USB4 V2) host router. The I/O tile on “Panther Lake-H” puts out four PCI-Express 5.0 lanes, eight PCI-Express 4.0 lanes, two Thunderbolt 5 ports, and an integrated Wi-Fi 7 + Bluetooth 5.4 controller.